先进封装解芯片难题-封装摩尔时代的突破

【原报告在线阅读和下载】:20260106【MKList.com】电子行业深度报告:先进封装解芯片难题-封装摩尔时代的突破 | 四海读报

【迅雷批量下载】:链接:https://pan.xunlei.com/s/VOXJ23RJHhoECPL5FRrVathfA1 提取码:umqb

【夸克批量下载】:链接:https://pan.quark.cn/s/fe42cc605010 提取码:j4Vv

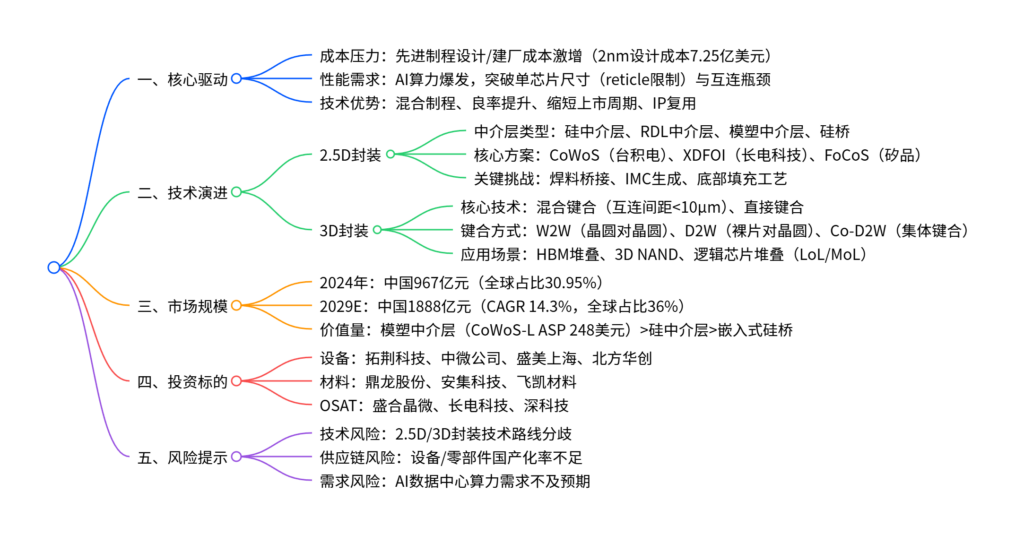

1. 一段话总结

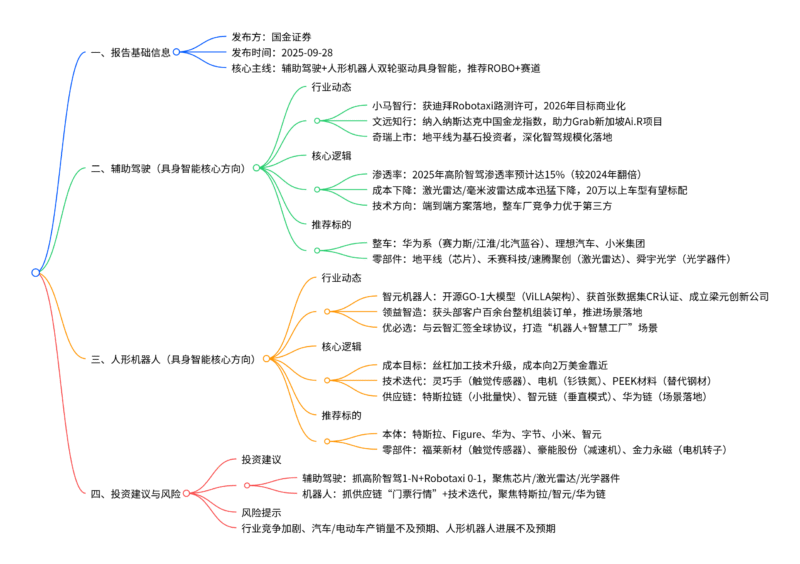

先进封装因先进制程成本指数级增长、AI算力需求爆发成为半导体行业突破方向,核心解决成本控制、芯片尺寸拓展、互连性能提升三大难题;技术上以2.5D封装(硅中介层、模塑中介层、硅桥) 和3D封装(混合键合、W2W/D2W键合) 为主,未来向“小芯片+异构集成+光学I/O”演进;2024年中国先进封装市场规模达967亿元,预计2029年增至1888亿元(2024-2029年CAGR 14.3%);投资机会集中在设备(键合机、CMP设备)、材料(混合键合材料、临时键合胶)、OSAT(封测企业) 三大环节,需警惕技术分歧、供应链国产化不足及AI需求不及预期风险。

2. 思维导图(mindmap)

3. 详细总结

一、核心驱动:先进封装成为半导体行业“破局关键”

-

先进制程边际效益下降

- 设计成本:2nm芯片设计成本达7.25亿美元,是65nm芯片的25倍;5nm工厂建设投资是20nm工厂的5倍。

- 良率困境:单芯片尺寸受光刻机reticle限制(约830mm²),超大芯片良率大幅下滑,成本激增。

-

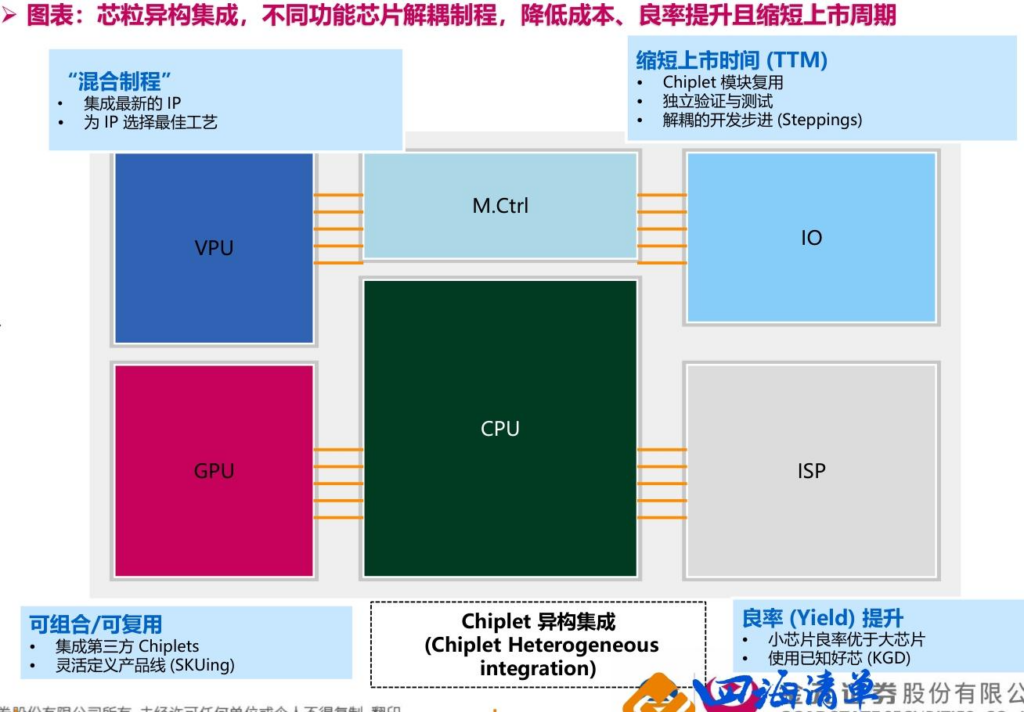

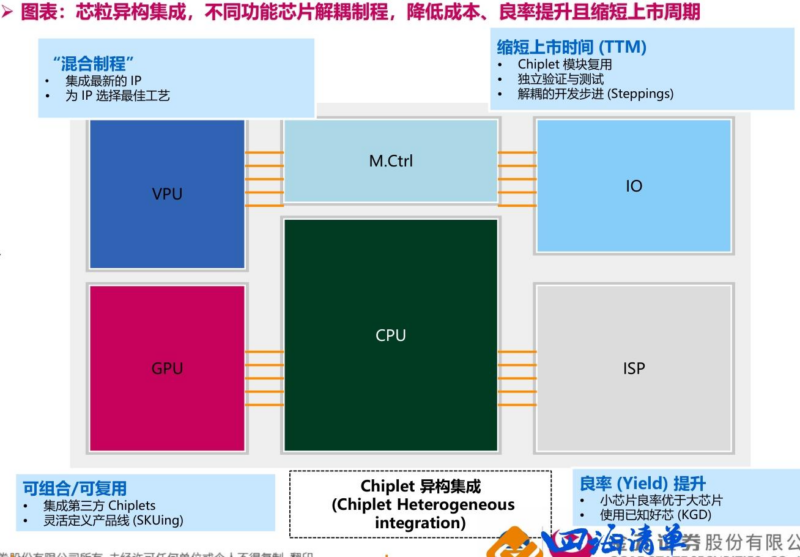

先进封装的核心价值

- 成本优化:通过“芯粒(Chiplet)+混合制程”,高性能模块用先进制程(如3nm CPU),I/O/模拟电路用成熟制程,降低整体成本。

- 性能拓展:突破单芯片尺寸限制,通过2.5D中介层、3D堆叠实现多芯片异构集成,满足AI芯片对算力、带宽的爆发式需求。

- 效率提升:IP可复用、独立验证,缩短产品上市周期(TTM),良率较单芯片显著提升。

二、技术演进:2.5D与3D封装并行发展

(一)2.5D封装:中介层为核心,硅桥成重要替代

-

技术原理:通过中介层(Interposer)实现多裸片并置互连,突破PCB/基板布线限制。

-

主流中介层类型对比

中介层类型 核心优势 局限 代表方案 硅中介层 布线密度高、信号完整性好 成本高、可扩展性差(≤3.3×reticle) 台积电CoWoS-S RDL中介层 无TSV、成本低、可扩展性强 互连性能稍弱 台积电CoWoS-R 模塑中介层 可扩展至>3.3×reticle,性能成本平衡 工艺复杂度高 台积电CoWoS-L 硅桥 局部高密度互连,替代硅中介层 布线密度低于模塑中介层 英特尔EMIB、长电科技XDFOI-B -

关键工艺:分为Chip First(技术成熟、成本低)和Chip Last(良率可控、适配多芯片),国内长电科技、盛合晶微已实现技术突破。

(二)3D封装:混合键合为核心,向高密度堆叠演进

-

技术痛点:2.5D封装受限于焊料凸点,互连间距难以低于20μm,存在焊料桥接、IMC生成等问题。

-

核心技术:混合键合(Hybrid Bonding)

- 原理:原子尺度实现电介质+金属(铜)直接连接,消除焊料层,互连间距<10μm。

- 优势:I/O密度高、带宽大、功耗低,封装高度缩减。

- 挑战:表面平坦化(Ra<0.5nm)、对准精度(<0.25μm)、高温退火(200-400℃)等技术门槛。

-

主流键合方式对比

键合方式 定义 优势 局限 应用场景 W2W 整片晶圆对键合 吞吐量高、洁净度易控制 良率耦合(90%良率堆叠4层仅65%) 3D NAND、HBM D2W 裸片(KGD)对晶圆键合 良率解耦、支持异构集成 吞吐量低、颗粒管理难 高端逻辑芯片堆叠 Co-D2W 裸片集体键合+晶圆对键合 兼顾W2W效率与D2W良率 工艺复杂 大规模异构集成

三、市场规模:AI驱动下高速增长

-

整体规模

- 2024年:中国先进封装市场967亿元,占全球30.95%;全球封测市场6495亿元,中国占比38.2%。

- 2029E:中国先进封装市场1888亿元,2024-2029年CAGR 14.3%,全球占比提升至36%;中国整体封测市场3900亿元,全球占比41.8%。

-

价值量分布

- 2.5D封装:模塑中介层(CoWoS-L)2025年ASP达248.33美元,高于硅中介层(CoWoS-S 174.3美元)。

- 3D封装:HBM封装2025年ASP 17.18美元,远高于3D NAND(2.57美元)、CBA DRAM(2.57美元)。

四、成本构成:不同技术路线差异显著

| 封装技术 | 核心成本项 | 成本占比 | 2025年ASP(美元) |

|---|---|---|---|

| 硅中介层(CoWoS-S) | 硅晶圆、TSV制造、微凸块 | 硅晶圆6%、TSV 4%、微凸块2% | 174.3 |

| 模塑中介层(CoWoS-L) | 模塑材料、RDL布线、硅桥 | RDL 44%、模塑+芯片52% | 248.33 |

| 3D堆叠(HBM) | 微凸块、堆叠工艺 | 微凸块36%、堆叠49% | 17.18 |

| 嵌入式硅桥(EMIB) | 硅桥、IC基板 | 硅桥22%、基板32% | 3.03 |

五、投资建议:聚焦设备、材料、OSAT三大环节

- 设备厂商:受益于键合、CMP、清洗等核心工艺设备需求,推荐拓荆科技(键合机)、中微公司(等离子体设备)、盛美上海(清洗设备)、北方华创(CMP设备)。

- 材料厂商:围绕混合键合材料、临时键合胶、抛光材料等,推荐鼎龙股份(抛光垫、PSPI)、安集科技(抛光液)、飞凯材料(环氧塑封料)。

- OSAT厂商:具备先进封装技术储备的封测企业,推荐盛合晶微(CoWoS类方案)、长电科技(XDFOI解决方案)、深科技(2.5D封装布局)。

六、风险提示

- 技术风险:2.5D与3D封装技术路线分歧较大,可能导致企业研发投入回报不及预期。

- 供应链风险:封装设备及核心零部件国产化率不足,设备供应可能受限。

- 需求风险:国内数据中心算力需求不及预期,拖累先进封装产业链需求。

4. 关键问题及答案

问题1:先进封装成为半导体行业焦点的核心驱动因素是什么?

- 答案:核心驱动来自成本、性能、效率三大维度。①成本端:先进制程(如2nm)设计成本达7.25亿美元,建厂投资是成熟制程的5倍,边际效益持续下降;②性能端:AI算力需求爆发,单芯片受光刻机reticle尺寸限制(约830mm²),难以满足算力/带宽需求,先进封装通过多芯片异构集成突破尺寸瓶颈;③效率端:芯粒(Chiplet)模式可复用IP、独立验证,缩短上市周期,同时小芯片良率显著高于大芯片,降低制造成本。

问题2:2.5D与3D封装的技术差异、核心优势及适用场景分别是什么?

- 答案:①技术差异:2.5D封装通过中介层(硅/RDL/模塑)实现裸片“平面并置互连”,互连间距20-50μm;3D封装通过混合键合/直接键合实现裸片“垂直堆叠互连”,互连间距<10μm。②核心优势:2.5D封装技术成熟、成本可控,可扩展性强;3D封装I/O密度更高、功耗更低、封装体积更小。③适用场景:2.5D封装适配AI GPU+HBM集成(如英伟达CoWoS)、中高端逻辑芯片;3D封装适配高密度存储堆叠(HBM、3D NAND)、高端逻辑芯片堆叠(如AMD 3D VCache)。

问题3:中国先进封装市场规模及投资机会分布在哪些环节?各环节的核心标的有哪些?

- 答案:市场规模方面,2024年中国先进封装市场967亿元,2029年预计增至1888亿元(CAGR 14.3%),全球占比从30.95%提升至36%。投资机会集中三大环节:①设备环节:聚焦键合机、CMP、清洗等核心设备,标的包括拓荆科技(键合机)、中微公司(等离子体设备)、盛美上海(清洗设备);②材料环节:围绕混合键合材料、抛光材料、塑封料等,标的包括鼎龙股份(抛光垫、PSPI)、安集科技(抛光液)、飞凯材料(环氧塑封料);③OSAT环节:具备先进封装技术储备的封测企业,标的包括盛合晶微(CoWoS类方案)、长电科技(XDFOI解决方案)、深科技(2.5D封装布局)。

暂无评论内容