【原报告在线阅读和下载】:书籍详情 | 四海读报

【迅雷批量下载】:链接:https://pan.xunlei.com/s/VOXJ23RJHhoECPL5FRrVathfA1 提取码:umqb

【夸克批量下载】:链接:https://pan.quark.cn/s/fe42cc605010 提取码:j4Vv

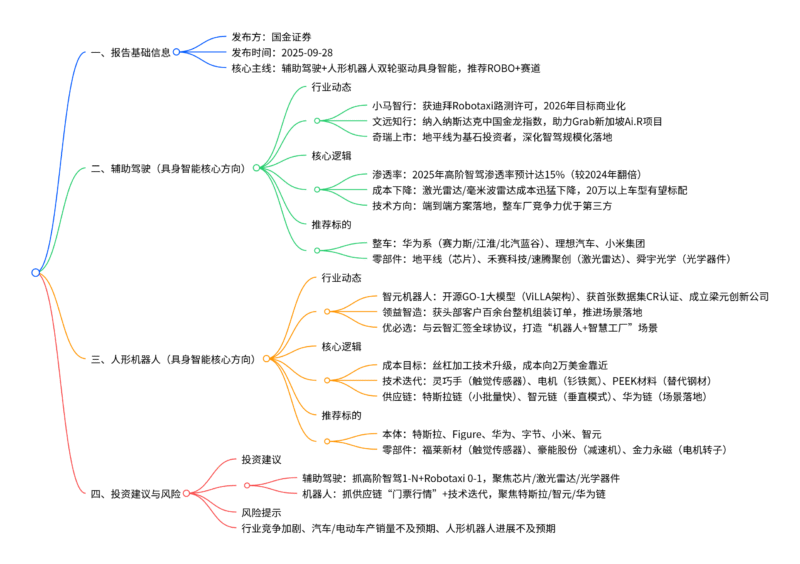

1. 一段话总结

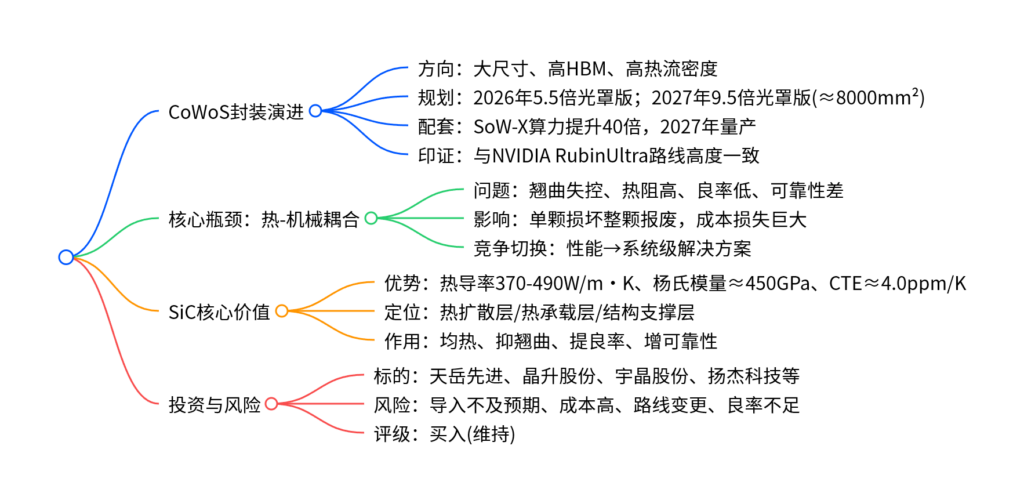

本文核心指出台积电CoWoS先进封装正迈向大尺寸、高HBM堆叠、高热流密度新阶段,行业瓶颈已从产能转向热管理与翘曲控制;SiC(碳化硅)凭借高热导率、高刚性、CTE与硅高度匹配的材料优势,有望以热扩散/热承载/结构支撑层切入破解瓶颈,即将进入产业放量期,计算机行业维持买入评级,并明确SiC衬底与设备相关投资标的。

2. 思维导图

3. 详细总结

一、CoWoS先进封装进入全新发展阶段

- 核心演进方向

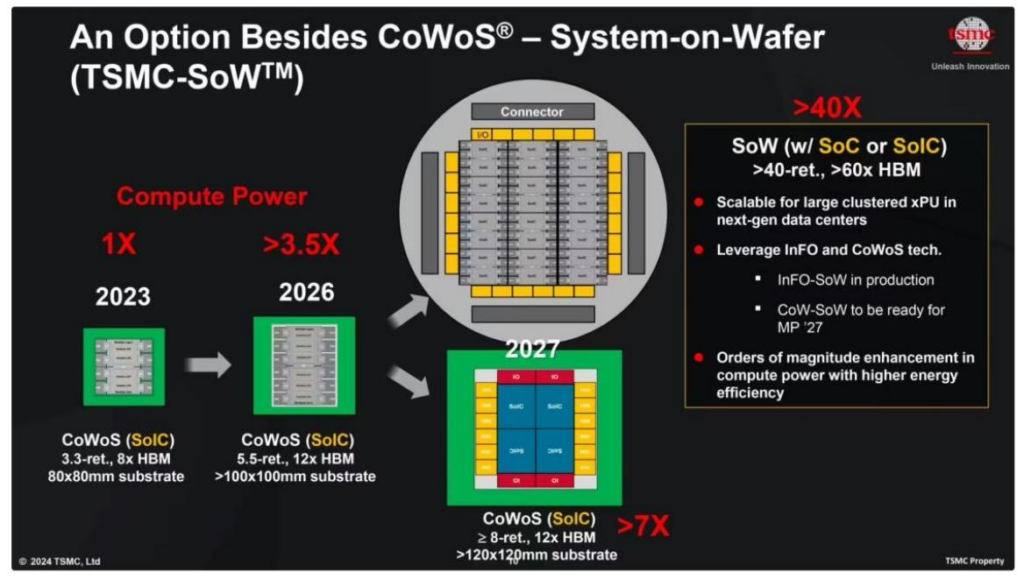

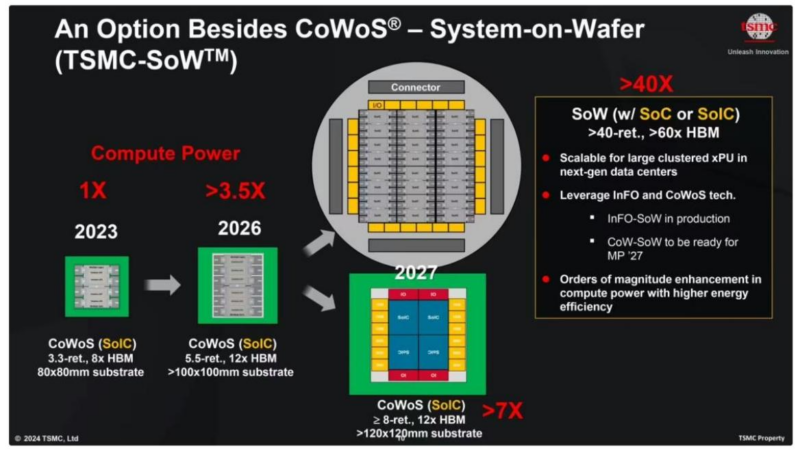

台积电明确CoWoS向大尺寸、高HBM堆叠、高热流密度升级,匹配AI大模型算力需求。 - 量产规划

- 2026年:推出5.5倍光罩尺寸过渡版本;

- 2027年:9.5倍光罩尺寸规模化量产,单封装有效面积≈8000mm²;

- 可支持:4颗3D堆叠芯片、12层及以上HBM、多颗逻辑芯片高密度集成。

- 同步技术

推出SoW‑X晶圆级系统集成方案,计算能力达现有CoWoS的40倍,2027年同步量产。 - 客户印证

与NVIDIA下一代RubinUltra芯片路线完全一致,先进封装成为决定AI算力上限的核心变量。

二、CoWoS瓶颈转向热管理与翘曲控制

- 核心矛盾转变

行业从产能约束转向热‑机械耦合可靠性问题,超大尺寸封装翘曲控制成为紧迫挑战。 - 关键问题

- 材料热膨胀系数(CTE)失配,引发翘曲、开路、锡球破裂、层间分层;

- 高端AI封装任一芯片损坏即整颗报废,良率波动带来巨额成本损失;

- 热阻控制、翘曲抑制、组装良率成为量产卡脖子环节。

- 竞争逻辑切换

从性能指标比拼→系统级解决方案竞争,低热阻材料、低翘曲基板、高精度装备环节显著受益。

三、SiC材料优势突出,切入先进封装黄金窗口期

-

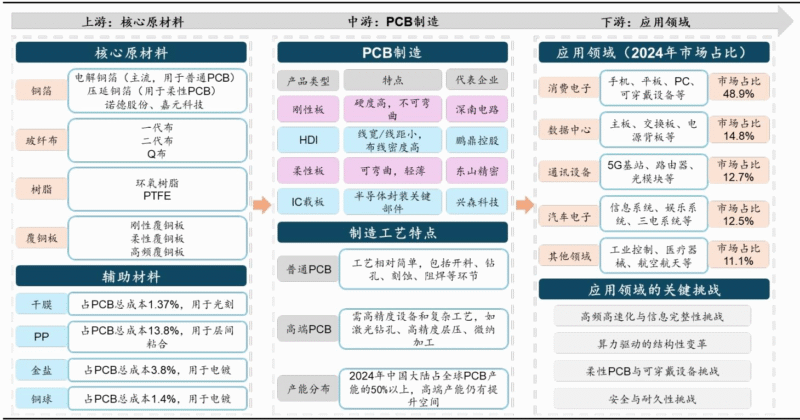

SiC核心材料参数对比

参数 4H‑SiC 硅中介层 有机RDL基板 核心优势 热导率 370‑490W/m·K ≈150W/m·K 0.2‑0.5W/m·K 散热能力提升2.5‑100倍 CTE ≈4.0×10⁻⁶/K ≈2.6×10⁻⁶/K 17‑50×10⁻⁶/K 与硅芯片高度匹配,降应力 杨氏模量 ≈450GPa 130‑170GPa 5‑10GPa 高刚性,强力抑制翘曲 莫氏硬度 9.0‑9.5 ≈7 2‑3 结构稳定、抗磨损 -

SiC导入定位

- 不替代主互连层,以热扩散层、热承载层、结构支撑层渐进导入;

- 适配110×110mm²超大尺寸CoWoS‑R方案,不改动现有RDL/Si中介层架构;

- 可应对数千瓦级功耗、局部热点超150℃的极端场景。

- 工程价值

- 快速均热,抑制热点积聚;

- 高刚性抑制翘曲形变,提升装配良率;

- 高温稳定,适配下一代散热架构。

四、投资建议与风险提示

- 行业评级:维持买入。

- 核心受益标的

SiC衬底及设备:天岳先进、晶升股份、宇晶股份、扬杰科技、华润微、三安光电。 - 风险提示

- SiC导入先进封装进度不及预期;

- SiC材料成本偏高,规模化受限;

- 先进封装技术路线变更;

- SiC封装良率与可靠性验证不及预期。

4. 关键问题与答案

问题1:为什么CoWoS超大尺寸封装会出现严重的翘曲与热管理问题?

答案:核心原因是芯片、中介层、基板之间热膨胀系数(CTE)严重失配,叠加功耗密度达到数千瓦级、局部温度超150℃,在高低温循环下产生剧烈翘曲;同时传统有机基板热导率极低,热量无法快速散出,最终导致良率下降、可靠性失效。

问题2:SiC为什么能解决CoWoS的热‑机械瓶颈,而不是直接替代硅中介层?

答案:SiC的核心优势是高热导率、高刚性、CTE与硅匹配,能同时解决散热和翘曲问题;但SiC无法实现主互连层所需的亚微米级高精度布线,且与现有CMOS产线不兼容,因此最优路径是作为热管理与结构支撑的非核心层切入,不改动现有成熟互连体系。

问题3:CoWoS技术演进对AI算力产业的核心影响是什么?

答案:CoWoS已从芯片配套环节升级为决定AI算力上限的核心变量,大尺寸、高HBM堆叠直接突破“内存墙”瓶颈,支撑算力指数级提升;同时热‑机械瓶颈倒逼材料与封装方案升级,SiC等新材料迎来产业放量机遇,产业链价值向热管理、先进材料环节重构。

© 版权声明

免费分享是一种美德,知识的价值在于传播;

本站发布的图文只为交流分享,源自网络的图片与文字内容,其版权归原作者及网站所有。

THE END

暂无评论内容